Introduction

Intel has a nice document.

Registers

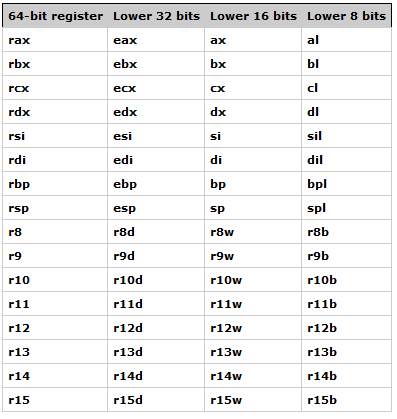

Integer

The initial 8 registers were expanded to 16 in x64. They were also widened to 64 bits.

Some have a legacy meaning:

- rax: accumulator

- rbx: base register

- rcx: count register

- rdx: data register

- rdi: destination index

- rsi: source index

- rsp: stacp pointer

- rbp: frame pointer

Special registers:

- flags: Table from here:

Bit Label Desciption

---------------------------

0 CF Carry flag

2 PF Parity flag

4 AF Auxiliary carry flag

6 ZF Zero flag

7 SF Sign flag

8 TF Trap flag

9 IF Interrupt enable flag

10 DF Direction flag

11 OF Overflow flag

12-13 IOPL I/O Priviledge level

14 NT Nested task flag

16 RF Resume flag

17 VM Virtual 8086 mode flag

18 AC Alignment check flag (486+)

19 VIF Virutal interrupt flag

20 VIP Virtual interrupt pending flag

21 ID ID flagMore info on register can be found here.

Floating point and MMX

There are 8 floating point 80-bit registers (FPR0-7) that overlap with the first of the 16 MMX 128-bit registers (XMM0-15).

Instruction types:

- Move operations: mov/movsxd (sign extension)/movzxd (zero extension)

- Subroutines: call/lock ret/push/pop

- lea: load effective address

- Arithmetic: add/sub/imul/inc/idiv

- Shift: shr/sal/shl/sar

- Rotate: rcr/rcl/rol/ror (with/out carry)

- Logic: and/or/xor/neg

- cmp

- jmp

- conditional jumps

- signed

- jge: Greater or equal

- jg

- je

- jne

- unsigned

- ja: Jump above

- jae: Jump above or equal

- jns

- jb: Jump below

- signed

- test

- cmov: Conditional move, based on a condition code below:

- cmove

- cmovb

- bt?

Floating point:

- cvttsd2si

- movsd

Calling conventions:

- Arguments in registers: rdi, rsi

- Return value: rax

Syntax

There are two syntaxes.

Intel:

mov eax, 5

add esp, 4

mov eax, [ebx + ecx*4 + mem_location]AT&T:

mov $5, %eax

addl $4, %esp

movl mem_location(%ebx,%ecx,4), %eax